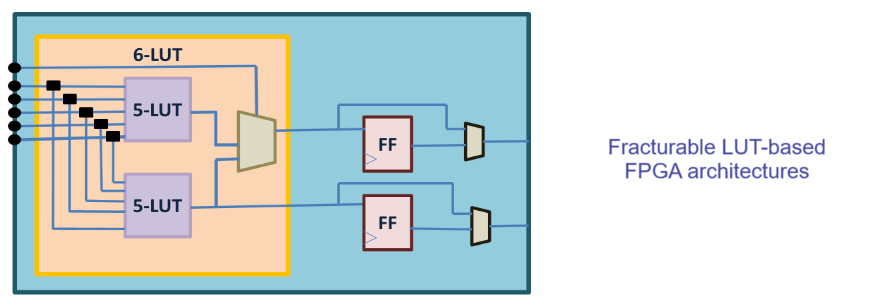

Area and delay trade offs in fracturable LUT-based FPGA architectures

Keywords:

Fracturable FPGA, Non-fracturable FPGA, Logic Blocks, look-up tables (LUTs)Abstract

Now-a-days, most commercial Field- Programmable Gate Arrays (FPGAs) are based on fracturable look-up tables (LUTs). A fracturable LUT based FPGA can operate in two modes: one without shared input and other with shared inputs. This paper investigates area and critical path delay of 6-LUT based fracturable FPGAs for different cluster sizes and cluster inputs. It is found experimentally that compared to non-fracturable 6-LUT based FPGAs, the fracturable 6-LUT based FPGAs with cluster sizes 7 to 10 show significant improvement in the area-delay results, with different chosen values of cluster inputs.

URN:NBN:sciencein.jist.2024.v12.733

Downloads

Downloads

Published

Issue

Section

URN

License

Copyright (c) 2023 Neeti, Sunita Dahiya

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

Rights and Permission