Evaluating the impact of cluster parameters on FPGA performance and density

Keywords:

Look-up table LUT, logic cluster, basic logic element BLE, CAD, field programmable gate array FPGA, cluster inputsAbstract

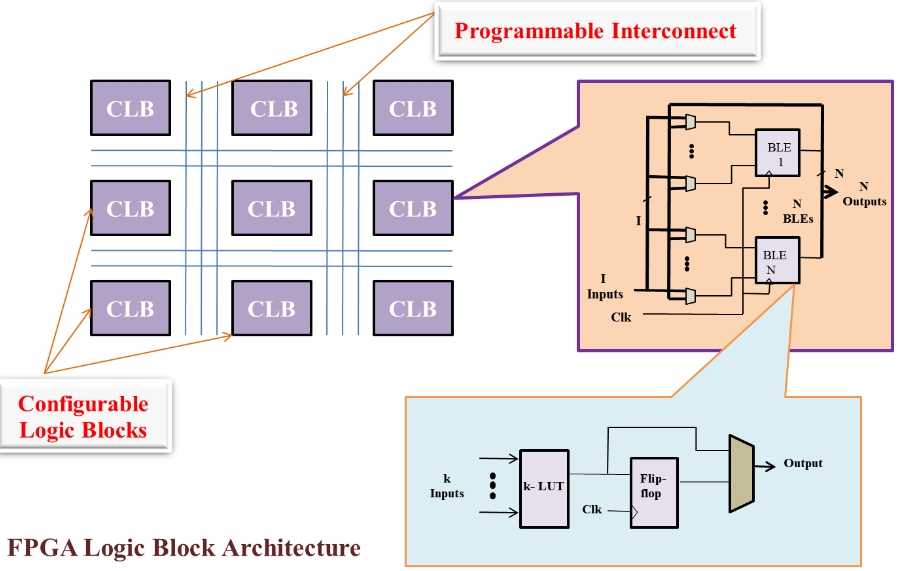

There has been a lot of preliminary investigation on the cluster-based Field Programmable Gate Arrays (FPGAs) to determine the cluster parameters that result in an efficient architecture in terms of area or speed or both. However, the advancement of technology and Computer Aided Design (CAD) tools provides numerous reasons to further explore FPGA clusters for possible improvements. This work investigates the area and speed performance of FPGA logic block architectures comprising clusters based on look-up tables (LUTs). Two crucial parameters of the cluster-based FPGA architectures are considered for investigation: the size of LUT (K) and the total inputs provided to a cluster (I). The LUT size is varied from 4 to 7 and the cluster inputs are varied from 40% of the total cluster inputs to their maximum permissible value. Experimentally, using VTR tool flow, it is found that the best area-delay trade-off is obtained for 4-input LUT based cluster using 80% of the maximum cluster inputs. It has been observed that some clusters exhibit better trade-off between area and delay with 70-80% of the total cluster inputs.

URN:NBN:sciencein.jist.2023.v11.520

Downloads

Downloads

Published

Issue

Section

URN

License

Copyright (c) 2023 Neeti, Sunita Dahiya

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

Rights and Permission