### Journal of Integrated SCIENCE & TECHNOLOGY

# Comparative performance evaluation of multi level inverter for power quality improvement

Chandra Bhushan Singh,1\* Abhimanyu Kumar,1 Chirag Gupta2

<sup>1</sup>Department of Electrical & Electronics Engineering, Vedica Institute of Technology, RKDF University, Bhopal, Madhya Pradesh, India. <sup>2</sup>Department of Electrical Engineering, Dr. A. P. J. Abdul Kalam University, Indore, Madhya Pradesh, India.

Received on: 28-Aug-2023, Accepted and Published on: 31-Oct-2023

### ABSTRACT

In recent times, multilevel inverters (MLIs) have emerged as a budget-friendly choice for various engineering applications that rely on renewable energy sources. These systems offer several advantages, such as simplified hardware

requirements, minimized switching losses, fewer switches, and improved output waveforms for voltage and current. One critical performance metric for MLIs is the lowering of total harmonic distortion. Due to these advantages, industries that employ MLI-based architectures have experienced significant expansion. This article provides an overview of different MLI configurations

Keywords: Multilevel Converters, Modulation Techniques, Power Electronics, MLI Topology, Harmonics, THD.

### **INTRODUCTION**

With the growing depletion of natural resources, RES is becoming more popular. Because of worldwide rapid urbanization as well as industrialization, the demand for electric power is likely to rise increasingly growth over the forecast period. Due to the cheap cost of coal, a considerable portion of power is now produced by fossils. Even as electricity production rises, so does the use of fragile energy sources. RES plays a role for the creation of electrical power to address the shortcomings connected with the production of electricity from carbon based fuels. The energy acquired out from sunlight is among the RES that may be utilized for such a reason (solar and wind). The PV-Cell technology can transform the sunlight into reliable electricity. A transistor substance is used to make solar (PV) modules.<sup>1</sup> The semiconductors type is selected for its capacity to collect a large amount of electrons. Silica is the most common compound semiconductor used in photovoltaic cells. Whenever a solar cell is exposed to direct sunlight, the radiation from the sun raises the activity levels of the particles in the silicon,

Corresponding Author: Chandra Bhushan Singh, Bhopal Email: cb9900276@gmail.com

Cite as: J. Integr. Sci. Technol., 2024, 12(2), 748. URN:NBN:sciencein.jist.2024.v12.748

©Authors CC4-NC-ND, ScienceIN ISSN: 2321-4635 http://pubs.thesciencein.org/jist causing energy to be generated. This is known as the photovoltaic effect. In order to transport electricity from the Photovoltaic panel to the demand, translators and converters are essential. In SMPS supply, several DC-DC conversion architectures including buckboosting and other converter are extensively utilized.<sup>2</sup> These conversions transform a voltage level to a specified voltage level, and they often provide a controlled output.<sup>3</sup> The fundamental power converters are buck and boost, and additional converter are developed from such two basic circuit topologies. Boost converters are the most common converters used to scale up the solar component's uncontrolled dc power to a specified greater constant supply level.<sup>4</sup> However, the majority of the workloads are powered by an AC source. Converter are being used to change a DC supply to an Ac supply. A circuitry that converts direct-current source (DC) to alternating (AC) is known as an inverters (AC). There's many different kinds of inverters, but multilevel inverters are by far the most popular due to their many advantages.

Numerous scientists have been motivated to develop a variety of power-converters, integrators, and controls as a result of this. Multilevel inverters (MLI) have attracted increased interest for use in renewable energy generating applications in power systems owing to its appealing properties of attaining maximum power, reducing voltage stress on the switch, and producing high output voltage gain with less harmonics. Because capacitor voltage sources usually offer greater than just few voltage levels, the MLI basic form is geared at producing a sine voltage. Because Multilevel inverter does have a low Total harmonic distortion and extremely low communication losses, it offers a wide spectrum of uses. MLI evolves into a useful and economical method for boosting energy and reducing Power to the load.<sup>5,6</sup>

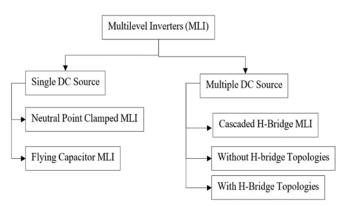

A multilevel inverter (MLI) is a power automated instrument that reconstructs a preferred sinusoidal waveform from many DC voltage sources as input. The resultant waveform nears sinusoidal waveform as the number of levels increases, and the resultant waveform quality improves with a significant decrease in Harmonic distortion. Multilevel inverters may work at higher voltages with less dv/dt than hard-switched two-level inverters. The set of input Dc voltage sources employed in the circuit is used to classify the three basic Multi-level inverter topologies. The multilevel inverters are divided into below categories:

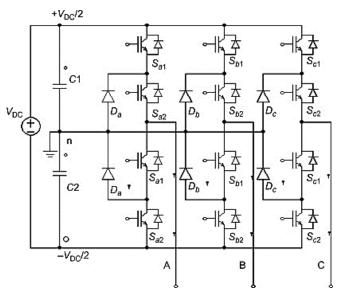

• A diode-clamped MLI is made up of a clamped diode, a capacitance, and a transistor switches (DC-MLI). This topology is distinguished through the application of diodes as a clamping device.

• Flying capacitor mli (FC-MLI): This form of inverter topologies is comparable to a diode clamped MLI in that it uses flying capacitors instead of diodes (DC-MLI). It requires the use of a capacitance that has been pre-charged. Pre-charging capacitors is essential, although it is tough to accomplish.

• No clamping resistive element or diodes are needed in a cascaded inverter (MLI). The main drawback of this MLI is that it necessitates a completely separate DC power source, increasing the total installation costs.

Although the aforementioned technique contains a large amount of clamping series capacitors and diodes, conventional modules have some disadvantages in terms of trying to balance the DC capacitor power output.<sup>7</sup> The number of transistors and inductances, and also the sophistication of the electricity hardware implementation, all raise installation costs as well as energy losses, but the shunt capacitor proposed inverter means allowing for fewer parts.<sup>8</sup>

Figure 1. Conventional Multilevel Inverter

Figure 2. Classification of Multilevel Inverter

Furthermore, the primary benefit about implementing such method is that it needs lesser switching devices and also no clamped diode or capacitance is required. To keep output current reliable, appropriate control approaches are being used. Pulse width modulation methodologies are used to create a switched capacitor MLI configuration with a cascaded inverter<sup>9</sup>. The objective of this research is to completely replace mli with a novel technique that can generate multiple voltage levels with fewer switching devices and power supply units<sup>10,11</sup>.

Table 1. Features and Limitations of Multilevel Inverters

| Туре                                                      | Feature                                                                                           | Limitations                                                                                |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Diode-<br>Clamped<br>Multilevel<br>Inverter<br>(DC-MLI)   | Diodes as<br>clamping<br>devices                                                                  | Limited output voltage.<br>Maintenance during<br>charging and discharging<br>are difficult |  |  |

| Flying<br>Capacitor<br>Multilevel<br>Inverter<br>(FC-MLI) | Capacitor                                                                                         | Pre-charging of capacitors                                                                 |  |  |

| Switched<br>Capacitor-<br>Fed<br>Multilevel<br>Inverter   | Switches,<br>Diodes and<br>capacitors.<br>Generate high<br>output voltage                         | High numbers of switches are required.                                                     |  |  |

| Cascaded<br>Multilevel<br>Inverter                        | Inductor, diode,<br>capacitors and<br>switches are<br>required.<br>High output<br>voltage gained. | Separate DC source.<br>Increased system cost.                                              |  |  |

### **Multilevel Inverters Topologies**

Inverters with multilevel were initially presented in 1975<sup>8</sup>, and since then, there's been a debated attempt to design multiple topologies that depend on dc voltage sources, along with modifying the network associated semiconductor switching configurations. Past study in this area aimed to achieve peak energy by using power

switching devices in a number of phases. It is also performed by converting energy and synthesizing energy in a cascade pattern utilizing several reduced dc voltage sources. The much more common sources of accepted voltages for individual and numerous interconnections RES are wind power, capacitance, and cells. MLI is shown in Fig. 2 depending on their network and general classification.

### Neutral Point Clamped MLI (NPC MLI)

In a 5 level Neutral Point Clamped MLI (NLP MLI)<sup>9</sup>, the c-link voltage is split equally among capacitance which are linked and put in line with identical high capacitor values. The point of reference has a dc buses half-way position which acts as a standard. For decreasing the rated power of switch, there really are four pairings of switching devices; all of them seem to be unidirectional, but every switching device is connected to an operating voltage of V/4 through clamping diodes. Whenever it relates to phasing, the NPC Multilevel inverter doesn't really imply separation. MLI is among the most often utilized topology in MV elevated situations due to its ease of efficiency and high device implementation. Hydraulic actuators, STAT-COM, Frequency control, and FAC-Transmission System, and a plethora of many other reduced frequencies applications, use it the most. It has extensive expertise with NPC Multi - level inverter issues, in addition to the many other fascinating themes. We may observe, for instance, that transmission lines distribution between switching device is unequal, and that semiconductors use is similarly inconsistent. Because of these shortcomings, operating NPC MLI at level of 5 or 7 may be challenging<sup>12</sup>.

#### Flying Capacitor MLI (FC MLI)

In a single-phase, five-level Flying Capacitor Multilevel Inverter (FC MLI), four DC-link capacitors are used, all having identical capacitance and voltage ratings. These capacitors effectively divide the DC bus voltage into four equal segments. Additionally, the system utilizes eight unidirectional switching devices for power supply. FC-MLI or a single dc-link capacitance voltages caps switch voltage, as well as the voltages grade allocation is consistent including all controls throughout this system. Among the most important features of FC Multilevel inverters is that it can use multiple internal dc voltages in clamping capacitors for charging balance. To keep charging or voltage levelling consistent across clamping capacitors, phasing redundancy are frequently utilized. For regulating charging levels across clamping capacitors, highfrequency switching is preferred. As an increased frequency MV traction driving entity, this concept has a wide range of applications. There are also multicell converters with FC-MLI.

### Cascaded H-Bridge MLI (CHB MLI)

In a 1- $\emptyset$  CHB MLI, pair of cells are coupled or connected in succession, and every cell contains an H-bridge including all 5 levels. Every H-bridge includes an independent dc power source with 4 unidirectional controls (switching device) for generating outputs of 3 levels of power. In order to eliminate verbosity in symmetrical CHB MLI, it is necessary to appropriately pick unequal dc voltage sources. This will allow for greater input voltages and the removal of the need for a large dc / dc sources. These asymmetrical topology employ ternary and quaternion sequence to choose the dc source. In comparison to a 5-level

Cascaded H-Bridge MLI, one of the key benefits of a 7 level asymmetrical Cascaded H-Bridge MLI is its verbosity, which is eliminated and the development of two more voltage levels. Even, this function is gained with the sacrifice of flexibility, and only becomes its major detriment. The arrangement of symmetric Cascaded H-Bridge MLI is exceptionally flexible in the operation of utilizing a smaller set of features in the process of developing a line voltage of the any amount, so this necessitates a simpler pulse generating strategy. As a consequence, this is often used in Photovoltaic system, rechargeable batteries uses, grid-tied devices, and a variety of many other application areas. The drawbacks of symmetric Cascaded MLI design are the primary demand for a large number of separate DC suppliers.

### **TOPOLOGIES WITH H-BRIDGE**

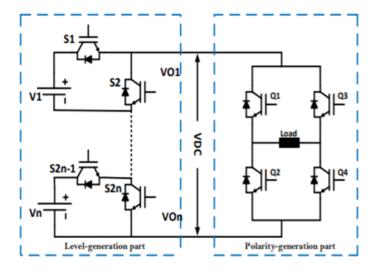

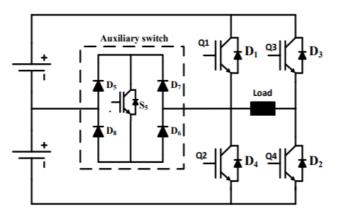

Gui Jia Su et, al.<sup>10</sup> has introduced CHB converter with multiple level DC Link (MLDCL). Fig 3 shows an MLDCL inverter dc source with two inputs. The MLDCL inverter is composed of a series of cascaded half-bridge units, which each involves a specific dc source and two series switches. Because the section of an inverter that creates a stepped dc voltage waveform is referred to as "level generation, such cascaded devices are re-ferred to as such. The H-Bridge is used to convert the resultant voltage polarities in terms of generating an accu-rate multi-level ac pulse. In compared to standard MLIs, the MLDCL has fewer switches for the same or equivalent output voltage levels<sup>13</sup>. The main benefit of this architecture is that it works with asymmetric source configuration. Permanent-magnet (PM) motor drives are one application area (100 kW) in the low-power range. A fast-switching silicon, such as Metal-Oxides Semiconductor Field - Effect transistors (MOSFETs), may be used for the leveller scheme, while an Insulated-Gate Bipolar Transistor can be used for the polarities generating component (IGBTs). The solar and fuel cell technologies are also incorporated in the MLDCL plan<sup>14</sup>.

Figure 3. Circuit Diagram for MLDCL Inverter

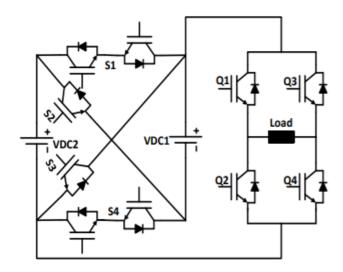

## Multiple Source based Switched Series/Parallel Sources (SSPS) based MLI Topology

Hinago et al<sup>15</sup> proposed a topology that is divided into two halves. The level-generation component contains dc voltage sources for producing a step dc voltage in the effects of positive polarities, and the polarities-generation component is responsible for converting the step dc voltage into AC voltages, as illustrated in Fig. 4. The fundamental advantage of this architecture is that it may operate in an asymmetrical arrangement. Furthermore, in compared to standard MLI topologies, it can deliver higher levels of output with fewer switching devices. An electric car in which the dc source is generated by a sequence of cells, and in which the SSPS is also used so that it could be new by the SSPS, resulting in the elimination of the requirement for power switches. Furthermore, in order to meet the traction needs in concurrently, it may connect various sources in a similarly flexible arrangement.

Figure 4. Circuit Diagram for SSPS Inverter

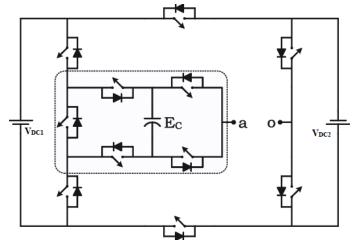

### Multiple Source based T-Type Inverter Topology

Gerardo Ceglia et al.<sup>16</sup> pioneered a novel form of inverter by using a five-level 1- $\emptyset$  inverter. The T-Type inverter's structure decreases the quantity of semiconductor components. In a 1- $\emptyset$  variant, as illustrated in Fig.5, there are two voltage sources.

Figure 5. Circuit Diagram for 5-level T-type Inverter

When compared to standard MLIs with the same number of levels, this design provides a substantial degree of benefit in terms of reduced switch number and reduced design complication.

This design results in a 40 percent reduction in the number of primary power switching devices required, as well as the elimination of diode and capacitance. An H-bridge with an auxiliary bi-directional switch is incorporated in this architecture for managing the connection of the dc supply in order to achieve the staircase voltage output. The asymmetric source configuration is not allowed by the architecture<sup>17</sup> since its design for the aim of gaining all of the required levels somehow doesn't offer switching states.<sup>17</sup>

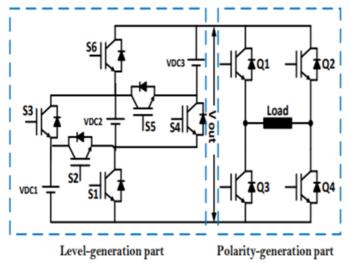

### Multiple Source based Crisscross Cascaded Multilevel Inverter topology

Khosroshahi et al.<sup>17</sup> proposed a novel architecture for the fundamental units in cascade, as illustrated in Fig. 6. In the design, there really are 2 dc power sources with unidirectional or bidirectional switching devices. This architecture has 2 components: one would be the primary foundation (level generation) while the other is the CHB (polarity generation). The power level-generation part's switches, S2 & S3, are unidirectional, while the other switches, S1, and S4, are for conducting bidirectional and bidirectional blocking switches of common emitter configuration. Both S1 and S4 contain a switch with two switches and accompanying drivers, and the polarity-producing section is made up of four power switches, i.e. (Q1, Q2, Q3, and Q4). One of the advantages of this topology is that the power switch count is lowered when compared to typical CHB multilevel inverters. Other advantages include a reduction in the number of separate dc voltage sources for an equivalent number of power switches in conventional topologies. In compared to the CHB multilevel inverter, the cost, voltage drop in output voltage, and volume of this design are all reduced in this manner.

Figure 6. Inverter Circuit Diagram for Crisscross Cascaded Inverter

### Series Connected Switched Sources (SCSS) based MLI topology

The foregoing technology, as illustrated in Fig. 7, essentially depends on switching devices to link sources in series. The energy semiconductor is connected to the reduced voltage supply poles during the upstream sources connection procedure. This connector may be used to provide a Multi-level voltage level, including both polarities being sent through an H-bridge. This architecture allows asymmetric setups to decrease the number of switching device, but the supply design must be symmetrical. The power semiconductors in this setup have differing ratings, which is a flaw. The load sharing is not possible due to the numerous configurations conveyed from the input stage. From Q1 through Q4, the higherrated switches must be changed at the frequency values feasible<sup>18</sup>. Multi - level inverter design based on MLI Modules (MLM) The topologies given by Babaei<sup>19</sup> is divided into two components, one for level production and one for polarities production. Switching device, power semiconductors, IGBTs, and the amount of voltage source inverter in this design may be decreased as the voltage output increases and grows. This topology's flaw is that it cannot run any asymmetrical arrangement. This topology's major need would be that it employs workloads with a large number of dc voltages and demands good power quality.

Figure 7. Inverter Circuit for Series Connected Switched Sources

### **RESULTS AND DISCUSSION**

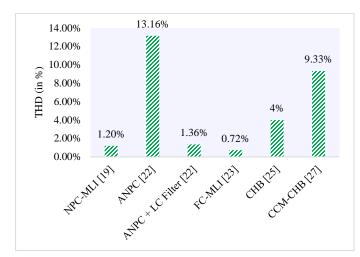

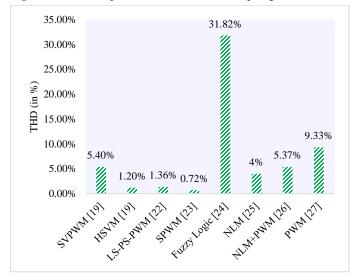

In this section various topologies their controls levels, THD, voltage gains are compared and illustrated in table 2.

The work reported by Annam et. al.<sup>17</sup> for NPC multilevel inverter conventional SV-pulse width modulator is used having three levels. The THD calculated for this is 5.4 % for NPC multilevel inverter controller HSVM, THD calculated is 1.2%. For boost NPC reported by Iqbal et. al.<sup>20</sup>, level shifted pulse width modulator is used having 7 level and the voltage gain is 1.5 %. Another topology discussed by Lee et. al.<sup>21</sup> named as active NPC also use level shifted SPWM, having 7 levels and the voltage gain calculator it is also 1.5 %, for nine levels the voltage gain decreases to 1% and for 11 levels the voltage gain again increases to 2.5%. another ANPC using level and phase shifted pulse width modulator having 11 level have THD of 13.16%. THD can be decreases by using LC filter with ANPC

| Topology Control Leve THD Voltag Ref                |                                          |    |            |        |                                   |

|-----------------------------------------------------|------------------------------------------|----|------------|--------|-----------------------------------|

|                                                     |                                          | 1  |            | e Gain |                                   |

| NPC-<br>MLI                                         | Conventiona<br>l SVPWM                   | 3  | 5.4%       | -      | $[14]^{1}$                        |

| NPC-<br>MLI                                         | HSVM                                     | 3  | 1.2%       | -      | $[14]^{1}_{7}$                    |

| BNPC<br>(Boost<br>NPC)                              | Level<br>shifted<br>PWM                  | 7  | -          | 1.5%   | $[17]^2_0$                        |

| ANPC<br>(Active<br>NPC)                             | Level<br>shifted<br>SPWM                 | 7  | -          | 1.5%   | [18] <sup>2</sup>                 |

| ANPC                                                | Level<br>shifted<br>SPWM                 | 9  | -          | 1%     | $[18]^2$                          |

| ANPC                                                | Level<br>shifted<br>SPWM                 | 11 | -          | 2.5%   | $[18]^2$                          |

| ANPC                                                | Level and<br>phase<br>shifted<br>PWM     | 11 | 13.16<br>% | -      | [15] <sup>1</sup><br><sup>8</sup> |

| ANPC +<br>LC Filter                                 | Level and<br>phase<br>shifted<br>PWM     | 11 | 1.36%      | -      | [15] <sup>1</sup><br><sup>8</sup> |

| FC-MLI                                              | SPWM                                     | 7  | 0.72%      | -      | [19] <sup>2</sup>                 |

| CHB<br>(Cascade<br>d H-<br>bridge)                  | Fuzzy Logic                              | 7  | 31.82<br>% | -      | $[19]^2$                          |

| СНВ                                                 | Nearest-<br>Level<br>Modulation<br>(NLM) | 19 | 4%         | -      | [20] <sup>2</sup>                 |

| CHB                                                 | NLM+PWM                                  | 9  | 5.37%      | -      | $[21]^2_4$                        |

| CCM-<br>CHB<br>(Cascade<br>d<br>Compact-<br>Module) | PWM                                      | 7  | 18.64<br>% |        | [22] <sup>2</sup><br>5            |

| CCM-<br>CHB                                         | PWM                                      | 13 | 9.33%      |        | [22] <sup>2</sup>                 |

topology reported by Abarzadeh et. al.<sup>18</sup> THD reduced to 1.36%, for FC multilevel inverter work reported by Azeem et.al.<sup>22</sup> using SPWM having 7 levels have minimum THD of 0.72%. THD is maximum for cascaded h-bridge topology using fuzzy logic controller having 7 levels fuzzy is 31.82%. Another cascaded h-

bridge used nearest level modulator as a controller and 19 levels THD calculated for this is 4%, work reported by Qanbari et.al.<sup>23</sup> The work proposed by Lee et.al.<sup>21</sup> in which CHB topology is used using nearest level pulse width modulator having 9 levels and THD calculated is 5.37 percent. For cascaded compact module given by Azeem et.al.<sup>22</sup> using pulse width modulator as a controller having 7 levels have THD of 18.64%. This topology also used with 13 levels and then THD drop to 9.3 %. The comparative analysis of THD is presented in Fig 8 for different MLI topologies and it was observed that FC-MLI had achieved lowest THD. Similarly, in Fig 9 author Babaei et.al.<sup>19</sup> the SPWM switching control had achieved lowest THD of 0.72%.

Figure 8. THD Comparison of Different MLI Topologies

Figure 9. THD Comparison of Different MLI Controls

### **CONCLUSION**

For DC-AC converter operations in the middle - high power levels, MLI''s are the best answer. The classic and modern Multi level inverter topology is discussed in this study. The MLI's fundamental components as well as applicability are thoroughly explained. Novel designs are presented to cut down on the number of elements, that has a huge influence on converter area, price, and performance. The benefits of using an asymmetrical dc power source to create these designs have increased their use in middle high power levels. The goal of improving Multilevel inverter effectiveness and less THD is made easier by variations in switching control. To address the growing need for renewable energy sources (RES) interfaces, MLI topology, switching control, and applicability studies are currently in development.

### **CONFLICT OF INTEREST STATEMENT**

There is no conflict of interest, financial or academic, for this article.

#### REFERENCES

- A. Sinha, K. Chandra Jana, M. Kumar Das. An inclusive review on different multi-level inverter topologies, their modulation and control strategies for a grid connected photo-voltaic system. *Solar Energy* **2018**, 170 (April), 633–657.

- C. Gupta, V.K. Aharwal. Optimizing the performance of Triple Input DC-DC converter in an Integrated System. *Journal of Integrated Science & Technology* 2022, 10 (3), 215–220.

- R.A. Krishna, L.P. Suresh. A brief review on multi level inverter topologies. Proceedings of IEEE International Conference on Circuit, Power and Computing Technologies, ICCPCT 2016 2016.

- C. Gupta, V.K. Aharwal. Design and simulation of Multi-Input Converter for Renewable energy sources. *Journal of Integrated Science & Technology* 2023, 11 (3), 1–7.

- A. Kumar, S. Jain. Multilevel Inverter with Predictive Control for Renewable Energy Smart Grid Applications. *International Journal of Electrical and Electronics Research* 2022, 10 (3), 501–507.

- A. Kumar, S. Jain. Predictive Switching Control for Multilevel Inverter using CNN-LSTM for Voltage Regulation. 2022, 11, 1–9.

- A. Perra. PWM Inverter Technology. *IEEE Aerospace and Electronic Systems Magazine* 1992, 7 (4), 20–22.

- G. Joos, X. Huang, B.T. Ooi. Direct-coupled multilevel cascaded series VAR compensators. *Conference Record - IAS Annual Meeting (IEEE Industry Applications Society)* 1997, 2, 1608–1615.

- H. Kuhn, N.E. Rüger, A. Mertens. Control strategy for multilevel inverter with non-ideal DC sources. *PESC Record - IEEE Annual Power Electronics* Specialists Conference 2007, 632–638.

- G.J. Su. Multilevel DC-link inverter. *IEEE Transactions on Industry* Applications 2005, 41 (3), 848–854.

- I. Colak, E. Kabalci, R. Bayindir. Review of multilevel voltage source inverter topologies and control schemes. *Energy Conversion and Management* 2011, 52 (2), 1114–1128.

- V. Jayakumar, B. Chokkalingam, J.L. Munda. A comprehensive review on space vector modulation techniques for neutral point clamped multi-level inverters. *IEEE Access* 2021, 9, 112104–112144.

- L.M. Tolbert, F.Z. Peng, T.G. Habetler. Multilevel inverters for electric vehicle applications. *IEEE Workshop on Power Electronics in Transportation* 1998, 79–84.

- 14. M. Toupchi Khosroshahi. Crisscross cascade multilevel inverter with reduction in number of components. *IET Power Electronics* **2014**, 7 (12), 2914–2924.

- Y. Hinago, H. Koizumi. A single-phase multilevel inverter using switched series/parallel DC voltage sources. *IEEE Transactions on Industrial Electronics* 2010, 57 (8), 2643–2650.

- G. Ceglia, V. Guzmán, C. Sánchez, et al. A new simplified multilevel inverter topology for DC-AC conversion. *IEEE Transactions on Power Electronics* 2006, 21 (5), 1311–1319.

- S.K. Annam, R.K. Pongiannan, N. Yadaiah. A Hysteresis Space Vector PWM for PV Tied Z-Source NPC-MLI with DC-Link Neutral Point Balancing. *IEEE Access* 2021, 9, 54420–54434.

- M. Abarzadeh, K. Al-Haddad. An Improved Active-Neutral-Point-Clamped Converter with New Modulation Method for Ground Power Unit

Application. *IEEE Transactions on Industrial Electronics* **2019**, 66 (1), 203–214.

- E. Babaei. A cascade multilevel converter topology with reduced number of switches. *IEEE Transactions on Power Electronics* 2008, 23 (6), 2657– 2664.

- A. Iqbal, M.D. Siddique, J.S.M. Ali, S. Mekhilef, J. Lam. A new eight switch seven level boost active neutral point clamped (8S-7L-BaNPC) inverter. *IEEE Access* 2020, 8, 203972–203981.

- S.S. Lee, C.S. Lim, K.B. Lee. Novel Active-Neutral-Point-Clamped Inverters with Improved Voltage-Boosting Capability. *IEEE Transactions* on Power Electronics 2020, 35 (6), 5978–5986.

- H. Azeem, S. Yellasiri, V. Jammala, B.S. Naik, A.K. Panda. A Fuzzy Logic Based Switching Methodology for a Cascaded H-Bridge Multi-Level Inverter. *IEEE Transactions on Power Electronics* 2019, 34 (10), 9360– 9364.

- T. Qanbari, B. Tousi. Single-Source Three-Phase Multilevel Inverter Assembled by Three-Phase Two-Level Inverter and Two Single-Phase Cascaded H-Bridge Inverters. *IEEE Transactions on Power Electronics* 2021, 36 (5), 5204–5212.

- 24. M.I. Sarwar, A. Sarwar, S.A. Farooqui, et al. A Hybrid Nearest Level Combined with PWM Control Strategy: Analysis and Implementation on Cascaded H-Bridge Multilevel Inverter and its Fault Tolerant Topology. *IEEE Access* 2021, 9, 44266–44282.

- S.S. Lee, M. Sidorov, N.R.N. Idris, Y.E. Heng. A Symmetrical Cascaded Compact-Module Multilevel Inverter (CCM-MLI) with Pulsewidth Modulation. *IEEE Transactions on Industrial Electronics* 2018, 65 (6), 4631–4639.